以皇晶TL2136B逻辑分析仪提供I2C信号测量解决方案

I2C 总线在电子产品中是很常见的一种总线,它的好处就是只需要两条线,就可以并联很多 IC 进行控制;但因为多装置(Device)及开路汲极(Open drain)的架构,常使I2C 总线除错工作变得困难。本文将提出一些实际的应用案例,并使用逻辑分析仪(Logic Analyzer)之各项功能,来协助排除问题。

使用转态储存进行长时间数据纪录

在 I2C总线讯号发生异常时,常无法明确的知道是哪个装置出错。因此,无法用设定触发的方式来做问题点的定位。使用者多半会考虑先把所有的波形都撷取回来再慢慢分析。但逻辑分析仪基本是以采样的方式撷取讯号,不管讯号有没有改变,都会随着采样撷取动作的进行,而不断地消耗内存。

而转态储存(Transitional Storage)功能是一种波形数据的储存模式,只在波形转态(Transition)的时候才将波形数据储存起来,这样当资料不转态时,逻辑分析仪就可以持续的等候且不存任何数据到内存内。相对于每个采样点都存一次资料的作法,转态储存将可以记下更多的数据。

I2C 的传输速度如下表一,整体来看速度都不会很快,因此会非常地适合使用转态储存,来拉长可储存的时间。

模式(mode) |

传输速度 |

Standard | 400 kbit/s |

Fast/Fast plus | 1 Mbit/s |

High speed | 3.4 Mbit/s |

举例来说,电路板上I2C 总线连接了装置 A 与装置 B,但在长时间烧机测试(Burn-In Test)的过程中,I2C 总线发生错误的问题。已知的现象是当发生错误时,I2C 总线上会出现无效的地址(Address),并且烧机的过程中会出现数次。

如何能利用逻辑分析仪来做问题厘清?这样的问题,若想把所有的波形数据都抓下来,其实是有困难的。 因为出现问题的时间点及次数都很不一定,且长达好

几天的烧机测试也使得把所有的数据都 Log 下来显得不切实际,又必须在大量的数据中寻找问题点。也是相当费时费力的工作。

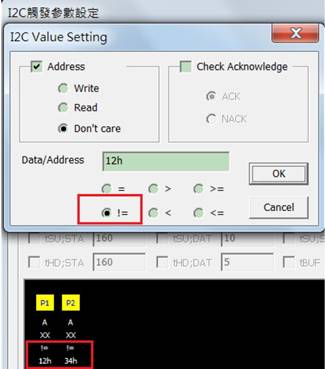

因此,可采用逻辑分析仪中的I2C 触发功能来进行定位。首先,先把装置 A(Addr:12h) 与装置 B (Addr:34h)的有效地址输入。 然后让逻辑分析仪找出不符合上述两个条件的地址。实际设定如图一所示。

图一 利用I2C 触发功能进行无效地址定位

然后再搭配逻辑分析仪撷取波形后自动储存功能,就很在烧机的过程中,每次触发成功就存盘,之后再检视存档波形之触发点即可。善用I2C 触发功能可以快速的协助波形定位,会比数据抓得多来的有意义很多。

同样的,善用整个使用I2C 参数来做为触发条件,例如地址符合或数据符合或多阶式的触发来指定更精准的触发,这些都是单纯使用边缘触发(Edge Trigger)所无法做到的功能。

I2C 触发检查时间违反(Timing violation)的问题点

I2C 总线会规范 SCL与 SDA 必须按规定时间送出,不然整个总线的行为将会发生错误,导致通讯失败。有时候实际波形的时间已经超出规格,但却无法在开发及验证被挑出来,因为有时候时间误差都不大,使得产品仍可正常使用。

但问题常常会留到量产时才爆发出来,造成量产不良率攀升,甚至到使用者手上才出现问题;这都是产品开发所不乐于见到的结果。

以图二所示,可启用逻辑分析仪之时间违反检查当作触发条件,设定所需检查的时间值,再让逻辑分析仪协助挑出时间违反的地方。逻辑分析仪系统采用 200MHz 采样率来进行采样。

因此,可检查之最小时间宽度为 5ns;这样就可以辅助使用者利用触发来做时间违反检查,非常适合于烧机测试时,用这个方式检测I2C 总线的讯号时间。

采用舒密特触发电路架构撷取质量良好的I2C 讯号

使用逻辑分析仪进行量测时,常会看到一些噪声。但使用示波器看的时候似乎又没有,是甚么原因?要如何排除?这是因为I2C 总线是开路汲极架构,总线上又同时接了很多装置,还有一些静电防护零件等等,可能使得I2C波形不见得会是很好的方波。

常见的I2C 波形如图三、四所示。但这样的波形在I2C 规范里面,是正常可接受的,并没有问题。

也因为这样,一般I2C芯片,都会规范在讯号输入脚位必须要有舒密特触发(Schmitt trigger)电路,以便于完善的解决讯号输入后能正确的处理逻辑讯号。为此,逻辑分析仪也可循此法做较完善的讯号解撷取动作。

图五为一般逻辑分析仪,此用单一个触发准位的方式来做逻辑0与逻辑1 的区分。这样的作法,很容易在待测讯号经过触发准位(Threshold)附近时,产生很多不可预期的逻辑变化。 使得撷取出来的讯号像是噪声或弹跳的现象。

若采用低通滤波(Low-pass filter)的做法,是可以滤除噪声,但又使得可能造成线路问题的高频噪声也同时被滤掉了。无论如何,这都不是适当的解决方案。

而图六则是启用了舒密特触发电路之后的画面,此架构采用了两组触发电压,分别为 Thres-high 与 Thres-low。两个电压间,就是所谓不转态区域,在这个区间内,不管讯号怎么改变,都不会影响逻辑判断。这样就可以正常的撷取到I2C 讯号,且真正的高频噪声也不会漏掉,也符合I2C 芯片设计规范。

堆栈示波器可同时看到I2C数字与模拟讯号

在使用了逻辑分析仪所提供的I2C总线触发与分析功能后。撷取下来的波形开始要进行问题分析阶段,常常很多项目都是软硬件共同合作,参与的人很多,若无法同时看到对应的模拟讯号,对于厘清问题帮助不大。尤其是线路造成的问题,数字讯号并无法清楚地呈现出问题点。

但是,单纯逻辑分析仪堆栈示波器并没有任何帮助,因为大部分的时候逻辑分析仪可以抓的时间长度会远大于示波器,这样,即使示波器显示波形出来,也不在正确的位置上。唯有透过逻辑分析仪的触发功能进行讯号定位,这样抓到的模拟讯号才是有意义的。

图七就是利用堆栈并设定触发之后同时抓到数字与模拟讯号,用户可以将它发送给需要看波形的人,I2C总线数字译码的部分可让用户快速理解他所看到波形。而模拟讯号的部分,则忠实的呈现出波形的原貌。两者这样的结合,成为最佳的量测方案。

推荐

-

QQ空间

腾讯微博

新浪微博

人人网

豆瓣